This article provides information on RISC-V specification, extensions and implementation example.

In my last article RISC, AVR, POWER , I discussed about RISC(Reduced Instruction Set Computing)and the various RISC architecture based cpu cores and devices. I would like to specify following Power Architecture books to understand similar concept in RISC-V :

- Book I (UISA) : User Instruction Set Architecture

- Book III (OEA): Operating Environment Architecture

- Book VLE : Variable Length Encoded Instruction

Key Takeaway

This session may be beneficial for a non-Computer Science background programmer to understand Integer, Fixed Point, Floating Point data types with C language.

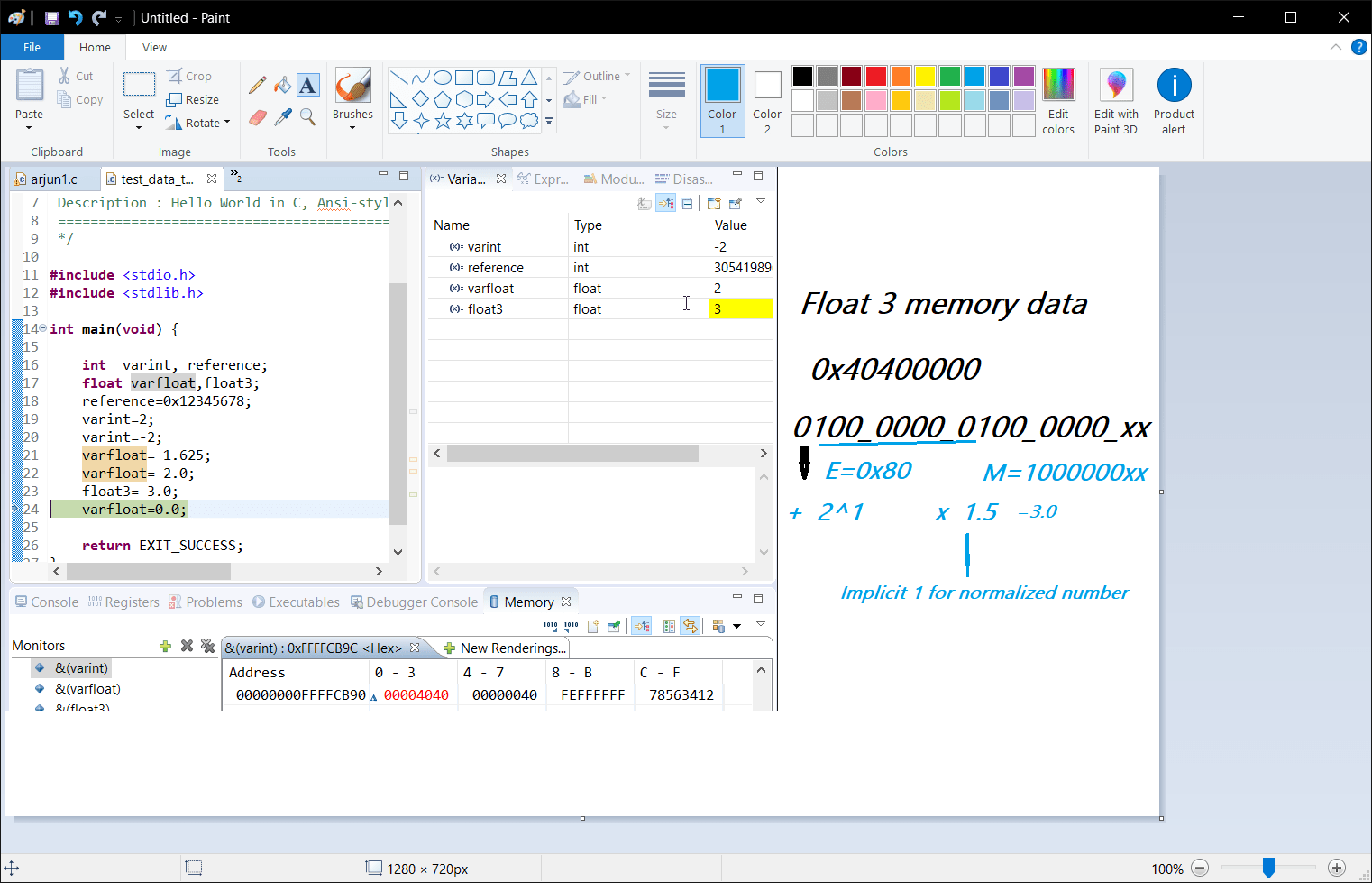

The floating calculation of 3.0 could not be completed in video recording, so providing here as correction :

One Engineering student asked me why so many data types. I use analogy with Airport traffic considering Airport as a cpu and other places as different peripherals. It works based on different kind of services. We can’t afford empty buses or overloaded cars. Similarly traffic between cpu and other peripherals depends on data transfer which depends on data structure and eventually on data elements.

I will also discuss the first Royalty Free Processor architecture which is aimed to be open source ISA for hardware design , similar to Linux for software. It is supposed to cover complete embedded horizon with backward compatibility software. It should be helpful to meet current challenges of a heterogeneous system.

RISC-V specificication

RISC-V ISA is divided into two parts

- User Level

- Privileged Level : It is designed to meet the operating system level protection.

User Level RISC-V (RV) ISA further divided into

- BASE

- Extension

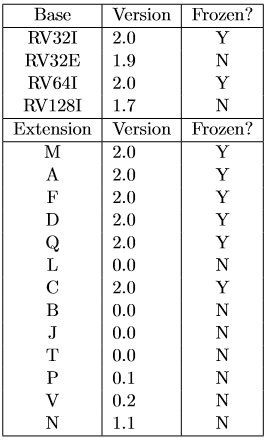

I am taking few of these as follows

- Integer (I) or Whole Number

- 32-bit : RV32I (Spec 2.0 Frozen)

- 64-bit : RV64I (Spec 2.0 Frozen)

- 128 -bit :RV128I

- RV32E : Reduced version of RV32I for Embedded MCUs

- Reduces the integer registers from 32 to 16 GPRs, (x0–x15)

- Removal of upper 16 registers saves around 25% core area with a corresponding core power reduction.

- Zero Register : RISC-V has a dedicated zero register (r0) which is hardwired to value 0 and can’t be modified. This is similar to MIPS and helps in logical computing with minimal hardware overhead. You may think it as a resistor is connected to ground.

- Multiplication and Division is named M (Spec 2.0 Frozen)

- Half Precision Floating Point IEEE-754 (H) 2008 is referred as binary16 . It will be part of extensions.

- Single Precision Floating Point(F) IEEE 754-(F) 2008 is referred as binary32 In C/C ++ it is defined as float , in FORTRAN as REAL and other as Single

The F extension adds 32 floating-point registers, f0–f31, each 32 bits wide, and a floating-point control and status register fcsr, which contains the operating mode and exception status of the floating-point unit

The D extension widens the 32 floating-point registers, f0–f31, to 64 bits (FLEN=64 in Figure 8.1). The f registers can now hold either 32-bit or 64-bit floating-point values

IEEE 754-2008 arithmetic standard

- Quad Precision Floating Point(Q)

- Decimal Floating Point IEEE 754-2008 (L)

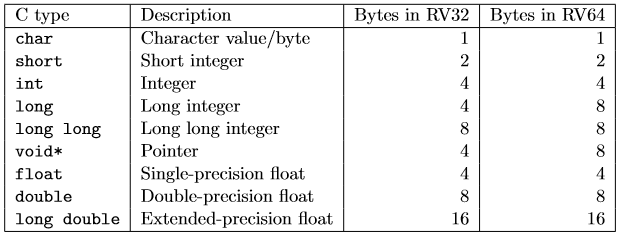

- What are corresponding C data types ?

Lets look into some interesting RISC-V extensions which makes this unique

- Compressed Instructions (C) :

The compressed instructions proposal for the RISC-V named “C”, is to reduce static and dynamic code size by adding 16-bit instructions for common operations. This is an extension to base ISA.

The compressed RISC ISA designs with mixed 16-bit and 32-bit instruction lengths (e.g., ARM Thumb2, microMIPS, PowerPC VLE) helps in reducing code size .

The philosophy of RVC is to reduce code size for embedded applications and to improve performance and energy-efficiency for all applications due to fewer misses in the instruction cache

- Dynamically Translated Language (J) is a proposal for future extension

Many popular languages are usually implemented via dynamic translation, including Java and JavaScript. These languages can benefit from additional ISA support for dynamic checks and garbage collection.

- Transactional memory extension (T)

This future extension is to support atomic operations involving multiple addresses. There is a proposal to include a small limited-capacity transactional memory buffer along the lines of the original transactional memory.

- Vector Operations(V)

This chapter presents a proposal for the RISC-V vector instruction set extension. The vector extension supports a configurable vector unit, to tradeoff the number of architectural vector registers and supported element widths against available maximum vector length

Naming conventions :

RISC-V ISA strings begin with either RV32I, RV32E, RV64I, or RV128I indicating the supported address space size in bits for the base integer ISA

Any example of RISC-V ISA implementation ?

India’s Shakti is a RISC-V chip developed at IIT Chennai. Here is the news about Linux booting on this. Here is the news about further development on this in India.

The first RISC-V processors were written as the Raven-1 test chip in 2011. RISCV organization maintains the list of cores and SoCs here.

Western Digital(WD) has announced its first RISC-V based core SweRV targeting Big Data and Fast Data market.

Recently MIPS also has announced to go open source.

Reference :

The RISC-V doc released under Creative Commons Attribution 4.0 International License.

“The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 2.2”, Editors Andrew Waterman and Krste Asanovi´c, RISC-V Foundation, May 2017.

This article is discussed at NextGen Program@RISC-V video .

Please subscribe to YouTube channel Embedkari for additional embedded related stuff.